# **DSP Project**

### **Reminder:**

Project proposals are due on Friday, October 19<sup>th</sup> by 5pm.

Budget: \$150/team.

# Registers

Registers are a general type of memory

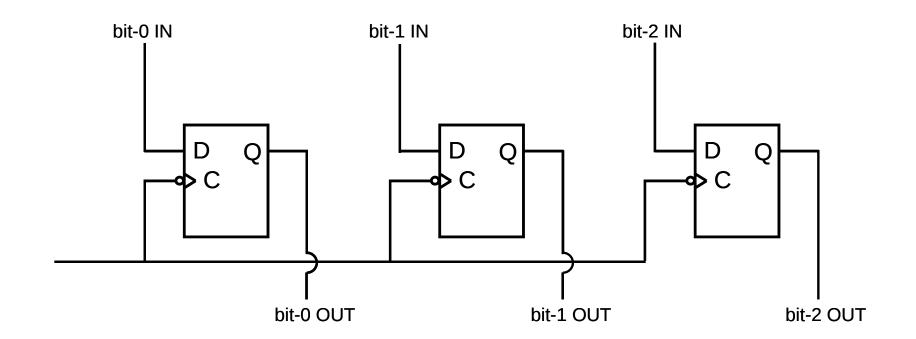

A Parallel In Parallel Out (PIPO) is very fast since eac bit is store or retrieved independently..

PIPO registers require a large number of input/output lines for storing large binary numbers.

## Registers

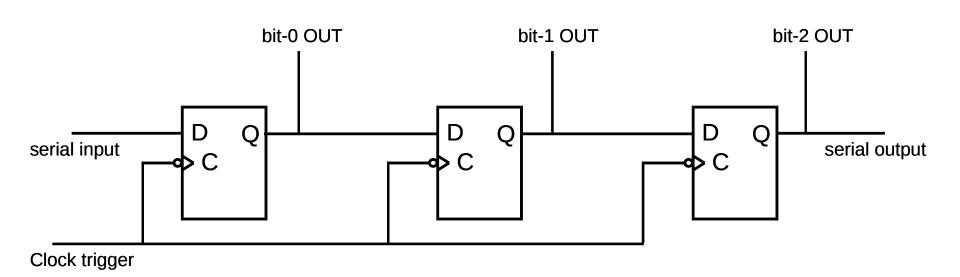

Shift Registers store serial information using a clock signal Single bits of data (0 or 1) are presented on the input with each clock cycle. The data can them be 'clocked out' one bit a time (as shown below) or in parallel.

Shift registers require only a few input/output lines.

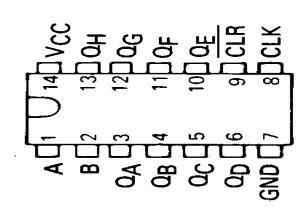

## 74LS164

- •The 74LS164 is a 8 bit parallel out Serial shift Register

- •The parallel output bits are labeled Q<sub>a-h</sub>

- ·Clocking of data occurs on the low to high level transition

- •A and B are serial inputs. A&B high sets data on clock 1

- ·Clear is asynchronous.

#### **FUNCTION TABLE**

|       | OUTPUTS  |   |   |                 |                     |                    |

|-------|----------|---|---|-----------------|---------------------|--------------------|

| CLEAR | CLOCK    | Α | В | $Q_{A}$         | $\alpha_{B}$        | Q <sub>H</sub>     |

| L     | Х        | Х | X | L               | L                   | L                  |

| Н     | L        | × | Х | Q <sub>A0</sub> | $oldsymbol{O}_{B0}$ | $Q_{H0}$           |

| н     | <b>↑</b> | н | Н | Н               | $Q_{An}$            | $Q_{Gn}$           |

| Н     | <b>↑</b> | L | X | L               | $Q_{An}$            | ${\tt Q}_{\sf Gn}$ |

| Н     | <b>↑</b> | Х | L | L               | Q <sub>An</sub>     | $Q_{Gn}$           |

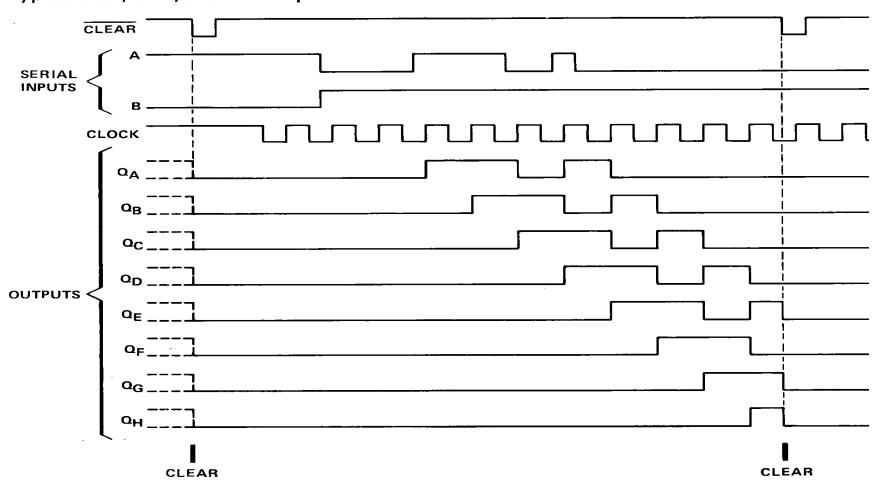

# 74LS164 Timing

typical clear, shift, and clear sequences

### **Multiplexers**

### What's a multiplexer?

A multiplexer is a generalized multi-input and multi-output gate. It will produce a specific multiple line output for each specific multiple line input.

**Example:** 3-line input and 4-line output (i.e. 3-to-4 multiplexer).

| А | В | С | 1 | 2 | 3 | 4 |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 |

N.B. Multiplexers can be very useful for converting a binary number to a HEX display code.

# **Multiplexers with FPGAs (Table)**

You could build a multiplexer out of logic gates ... or you could let the Verilog compiler figure it out.

#### N-to-1 multiplexer:

```

mux_primitive.v

primitive mux primitive(out1, A, B, C);

// 3-to-1 multiplexer

input A, B, C;

// 3 input wires

output out1;

// 1 output wire

table

// table defines the output based on the 3 inputs

// A B C out1

000:0;

001:0;

010:0;

100:1;

10

11

110:1;

12

0 1 1 : 0 ;

13

101:1;

111:0;

14

endtable

15

16

17

endprimitive

18

```

## **Multiplexers with FPGAs (if)**

An always block with "if" statements can be used for an N-to-M multiplexer:

```

mux_always_if.v

module mux always if (input 3bit, output 4bit); // 3-to-4 multiplexer

input [2:0] input 3bit;  // 3 input lines (bits)

output reg [3:0] output 4bit; // 4-bit output register

// always block with "if" statement for each input case

always

begin

8

if (input 3bit == 3'b000) output 4bit <= 4'b0001;

if (input 3bit == 3'b001) output 4bit <= 4'b0010;

9

if(input 3bit == 3'b010) output 4bit <= 4'b0100;

10

if (input 3bit == 3'b100) output 4bit <= 4'b1000;

11

12

if (input 3bit == 3'b110) output 4bit <= 4'b1100;

if (input 3bit == 3'b011) output 4bit <= 4'b0110;

13

if (input 3bit == 3'b101) output 4bit <= 4'b1010;

14

if (input 3bit == 3'b111) output 4bit <= 4'b0001;

15

16

end

17

endmodule

18

```

An always block guarantees that you won't have any signal races or glitches.

## **Multiplexers with FPGAs (case)**

An always block with "case" constructs can be used for an N-to-M multiplexer:

```

module mux always case(input 3bit,output 4bit); // 3-to-4 multiplexer

1

2

input [2:0] input_3bit;  // 3-bit input

output reg [3:0] output 4bit; // 4-bit output

3

4

5

always

// always block with "case" construct

6

begin

case (input 3bit)

3'b000: output 4bit <= 4'b0001;

8

3'b001: output 4bit <= 4'b0010;

9

3'b010: output 4bit <= 4'b0100;

10

3'b100: output 4bit <= 4'b1000;

11

3'b110: output 4bit <= 4'b1100;

12

13

3'b011: output 4bit <= 4'b0110;

14

3'b101: output 4bit <= 4'b1010;

15

3'b111: output 4bit <= 4'b0001;

16

endcase

17

end

18

19

endmodule

```

### **Multiple Modules**

```

multiple_modules.v

module multiple modules(input clock, output FourBits); // top-level module

2

input input clock;

// input wire

output [3:0] output FourBits; // output wires

3

wire [2:0] counter output; // output wires of counter

wire [2:0] mux input;

// input wires of multiplexer

8

assign mux input = counter output; // connect the counter output and multiplexer input wires

9

// call the "counter" module

10

counter counter result (input clock, counter output);

// with instance "counter result"

11

12

mux always case mux output (mux input, output FourBits); // call the "mux always case" module

13

// with instance " mux output"

14

15

16

endmodule

mux_always_case.v*

17

module mux always case(input 3bit,output 4bit); // 3-

input [2:0] input 3bit; // 3-bit input

output reg [3:0] output 4bit; // 4-bit output

counter.y

// always block with "case" construct

always

module counter (input clk, output 3bit);

begin

2

input input clk;

case(input 3bit)

output reg [2:0] output 3bit;

3'b000: output 4bit <= 4'b0001;

3'b001: output 4bit <= 4'b0010;

9

always@(posedge input clk)

10

3'b010: output 4bit <= 4'b0100;

3'b100: output 4bit <= 4'b1000;

11

output 3bit <= output 3bit + 3'b001;

3'b110: output 4bit <= 4'b1100;

12

8

13

3'b011: output 4bit <= 4'b0110;

9

3'b101: output 4bit <= 4'b1010;

14

10

endmodule

3'b111: output 4bit <= 4'b0001;

15

11

16

endcase

17

end

18

19

endmodule

20

```

### **Multiple Modules**

```

multiple_modules.v

module multiple modules(input clock, output FourBits); // top-level module

2

input input clock;

// input wire

output [3:0] output FourBits;

// output wires

3

Wires for connecting the 2 lower level modules

5

wire [2:0] counter output;

/ output wires of counter

wire [2:0] mux input;

input wires of multiplexer

6

8

assign mux input = counter output: /// connect the counter output and multiplexer input wires

9

10

counter counter result(input clock, counter output);

// call the "counter" module

// with instance "counter result"

11

module name instance name

12

mux always case mux output (mux input, output FourBits); // call the "mux always case" module

13

// with instance " mux output"

14

15

16

endmodule

mux_always_case.v*

17

module mux always case(input 3bit,output 4bit); // 3-

input [2:0] input 3bit;  // 3-bit input

output reg [3:0] output 4bit; // 4-bit output

counter.y

// always block with "case" construct

always

module counter (input clk, output 3bit);

begin

2

input input clk;

case (input 3bit)

output reg [2:0] output 3bit;

3'b000: output 4bit <= 4'b0001;

3'b001: output 4bit <= 4'b0010;

9

always@(posedge input clk)

10

3'b010: output 4bit <= 4'b0100;

3'b100: output 4bit <= 4'b1000;

11

output 3bit <= output 3bit + 3'b001;

3'b110: output 4bit <= 4'b1100;

12

13

3'b011: output 4bit <= 4'b0110;

9

3'b101: output 4bit <= 4'b1010;

14

10

endmodule

3'b111: output 4bit <= 4'b0001;

15

11

16

endcase

17

end

18

19

endmodule

20

```

## **Multiple Modules**

```

multiple_modules.v

module multiple modules(input clock, output FourBits); // top-level module

2

// input wire

inpuc clock,

output [3:0] output FourBits;

// output wires

3

4

Warning: DO NOT make these registers !!!

5

wire [2:0] counter output;

wire [2:0] mux input;

// input wires of multiplexer

assign mux input = counter output; // connect the counter output and multiplexer input wires

8

9

10

counter counter result(input clock, counter output);

// call the "counter" module

// with instance "counter result"

11

module name instance name

12

mux always case mux output (mux input, output FourBits); // call the "mux always case" module

13

// with instance " mux output"

14

15

16

endmodule

mux_always_case.v*

17

module mux always case(input 3bit,output 4bit); // 3-

input [2:0] input 3bit;  // 3-bit input

output reg [3:0] output 4bit; // 4-bit output

counter.y

// always block with "case" construct

always

module counter (input clk, output 3bit);

begin

2

input input clk;

case(input 3bit)

output reg [2:0] output 3bit;

3'b000: output 4bit <= 4'b0001;

3'b001: output 4bit <= 4'b0010;

9

always@(posedge input clk)

3'b010: output 4bit <= 4'b0100;

10

11

3'b100: output 4bit <= 4'b1000;

output 3bit <= output 3bit + 3'b001;

3'b110: output 4bit <= 4'b1100;

12

8

end

13

3'b011: output 4bit <= 4'b0110;

9

3'b101: output 4bit <= 4'b1010;

14

10

endmodule

3'b111: output 4bit <= 4'b0001;

15

11

16

endcase

17

end

18

19

endmodule

```

20